?電快速瞬變脈沖群抗擾度測試

電快速瞬變脈沖群抗擾度測試

電快速瞬變脈沖群抗擾度試驗也叫EFT電快速脈沖測試�,是一種將由許多快速瞬變脈沖組成的脈沖群耦合到電氣和電子設(shè)備的電源端口、信號和控制端口并觀察被測設(shè)備在遭受這些脈沖干擾時對原有性能保持程度的一種測試���。

試驗的目的就是為了檢驗電子��、電氣設(shè)備在遭受這類暫態(tài)騷擾影響時的性能����。通過測試對電氣和電子設(shè)備在受到重復(fù)性快速瞬變脈沖群干擾時的性能進行評定����。

測試標(biāo)準(zhǔn)

GB/T 18595-2014 《一般照明用設(shè)備電磁兼容抗擾度》

CISPR 14-2:2015、EN 55014-2:2015 《家用電器��、電動工具和類似器具的電磁兼容要求 第 2 部分:抗擾度》

GB/T 17626.4-2018���、IEC 61000-4-4:2012���、EN 61000-4-4:2012 《電磁兼容試驗和測量技術(shù) 電快速瞬變脈沖群抗擾度試驗》

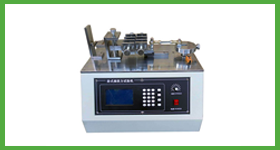

測試設(shè)備

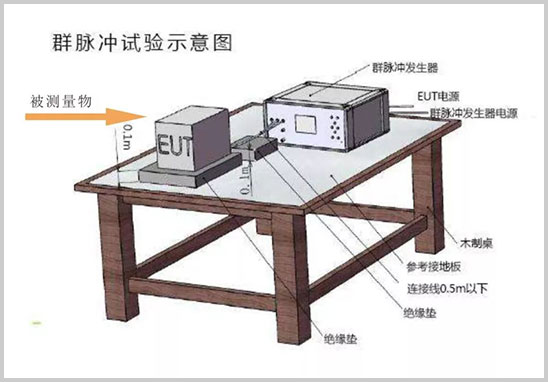

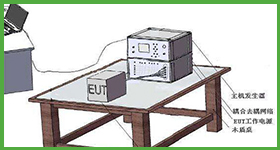

試驗發(fā)生器(包含測量和校準(zhǔn)裝置)、耦合裝置����、去耦網(wǎng)絡(luò)、接地參考平面等�����。

測試環(huán)境

溫度:15℃-35℃�、濕度:30%-65%、氣壓:68kpa-106kpa�����;與靜電抗擾度測試條件相同����。

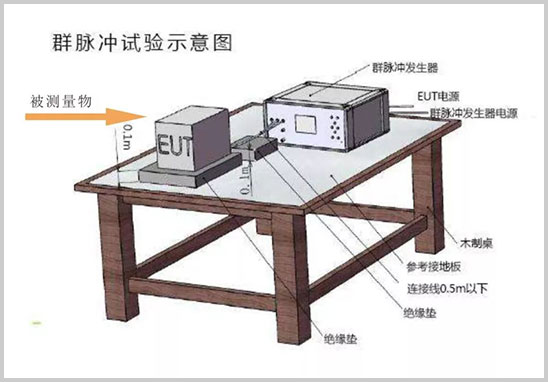

測試場地示意圖

電快速瞬變脈沖群抗擾度試驗相關(guān)問題的改進建議

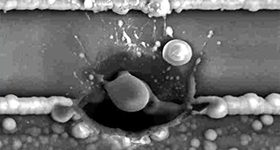

(1)針對電快速脈沖群干擾試驗出現(xiàn)的問題���,主要可以采取濾波及吸收的辦法來實現(xiàn)對電快速瞬變脈沖的抑制;

(2)在設(shè)備設(shè)計初期就應(yīng)重點考慮抑制電快速瞬變脈沖群干擾設(shè)計�;

(3)在PCB層電源輸入位置要做好濾波,通常采用的是大小電容組合��,根據(jù)實際情況可以酌情再添加一級磁珠來濾除高頻信號�����,盡量采用表面封裝��;

(4)盡量減小PCB的地線公共阻抗值��;

(5)PCB布局盡量使干擾源遠(yuǎn)離敏感電路�;

(6)PCB的各類走線要盡量短;

(7)減小環(huán)路面積�;

(8)在綜合布線時要注意強弱電的布線隔離、信號線與功率線的隔離��。綜合布線是系統(tǒng)很重要的一個設(shè)計組成部分��,一個糟糕的綜合布線格局很可能斷送一個設(shè)計精良的PCB的穩(wěn)定性��;

(9)關(guān)鍵敏感芯片需要屏蔽;

(10)元器件的選擇上應(yīng)使用質(zhì)量可靠的芯片���,最好做過芯片級的電磁兼容仿真試驗����,質(zhì)量可靠的電器元件選用可提升對電快速瞬變脈沖信號的抑制能力�。

辦理電快速瞬變脈沖群抗擾度試驗�����,請聯(lián)系第三方EMC檢測機構(gòu)-優(yōu)科檢測認(rèn)證�。 我們將以優(yōu)惠的價格和周到的服務(wù)為您提供專業(yè)高效的檢測認(rèn)證服務(wù)。 如果您向我們提供產(chǎn)品圖片和規(guī)格����,我們將根據(jù)您的產(chǎn)品給出相應(yīng)的周期、報價和具體方案��。 歡迎您來電咨詢���!

在線留言

如果您對我司的產(chǎn)品或服務(wù)有任何意見或者建議����,您可以通過這個渠道給予我們反饋。您的留言我們會盡快回復(fù)����!

掃碼咨詢

掃碼咨詢

微信訂閱號

微信訂閱號